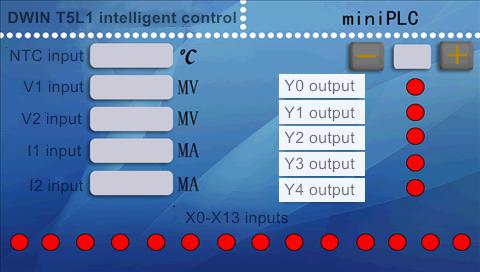

Iċ-ċipep dual-core tas-serje DWIN T5L għandhom il-karatteristiċi ta 'frekwenza ewlenija għolja u kapaċità qawwija ta' pproċessar ta 'immaġni, li jistgħu jintużaw biex jibnu mikro PLC u jipproċessaw applikazzjonijiet HMI.Din is-soluzzjoni PLC hija bbażata fuq iċ-ċippa T5L1, l-introduzzjoni bażika hija kif ġej:

1. Funzjoni Bażika

14-il input ta 'swiċċ diġitali, b'iżolament ta' optocoupler;

8 kanali ta 'input analogu ta' 0 ~ 10V (0 ~ 20mA);

6 outputs relay;

Output analogu PWM b'2 kanali (tista 'żżid output DAC);

Appoġġ 485 komunikazzjoni, komunikazzjoni CAN, komunikazzjoni TTL;

Appoġġ input u output tal-polz b'veloċità għolja, provvista ta 'enerġija industrijali ta' 24V

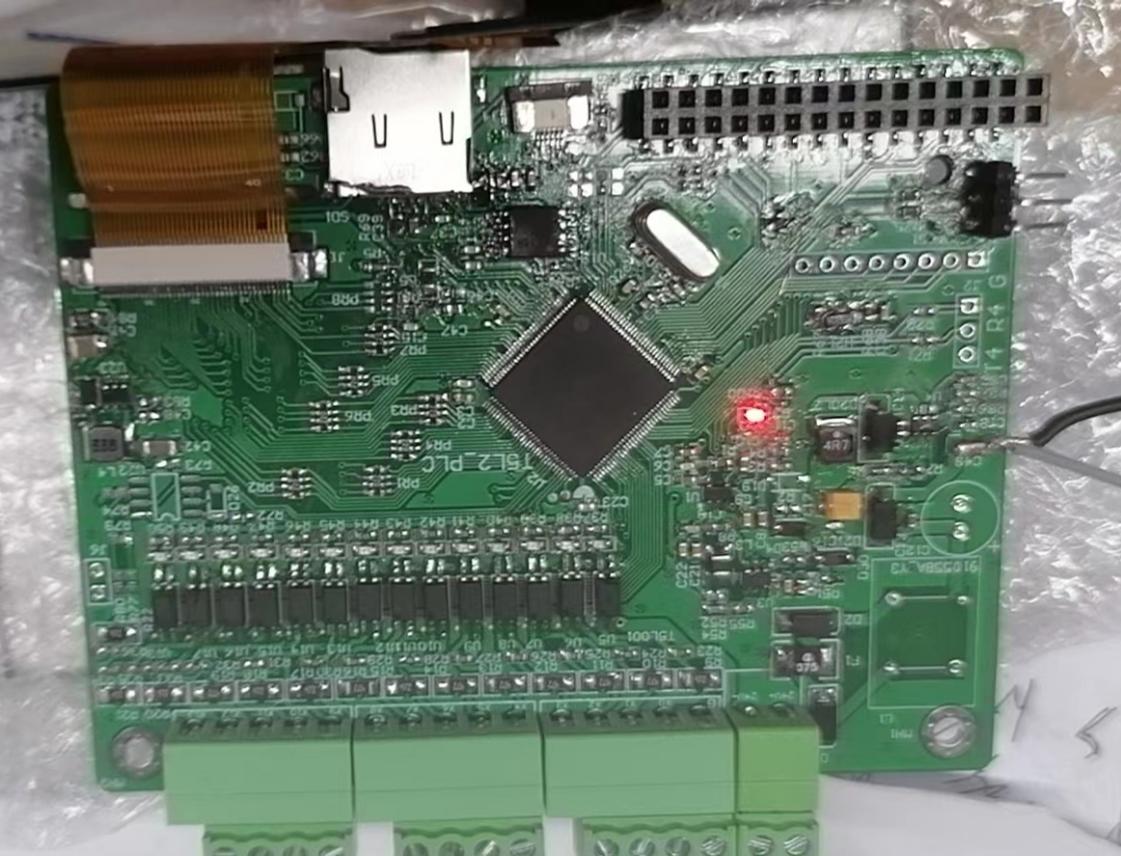

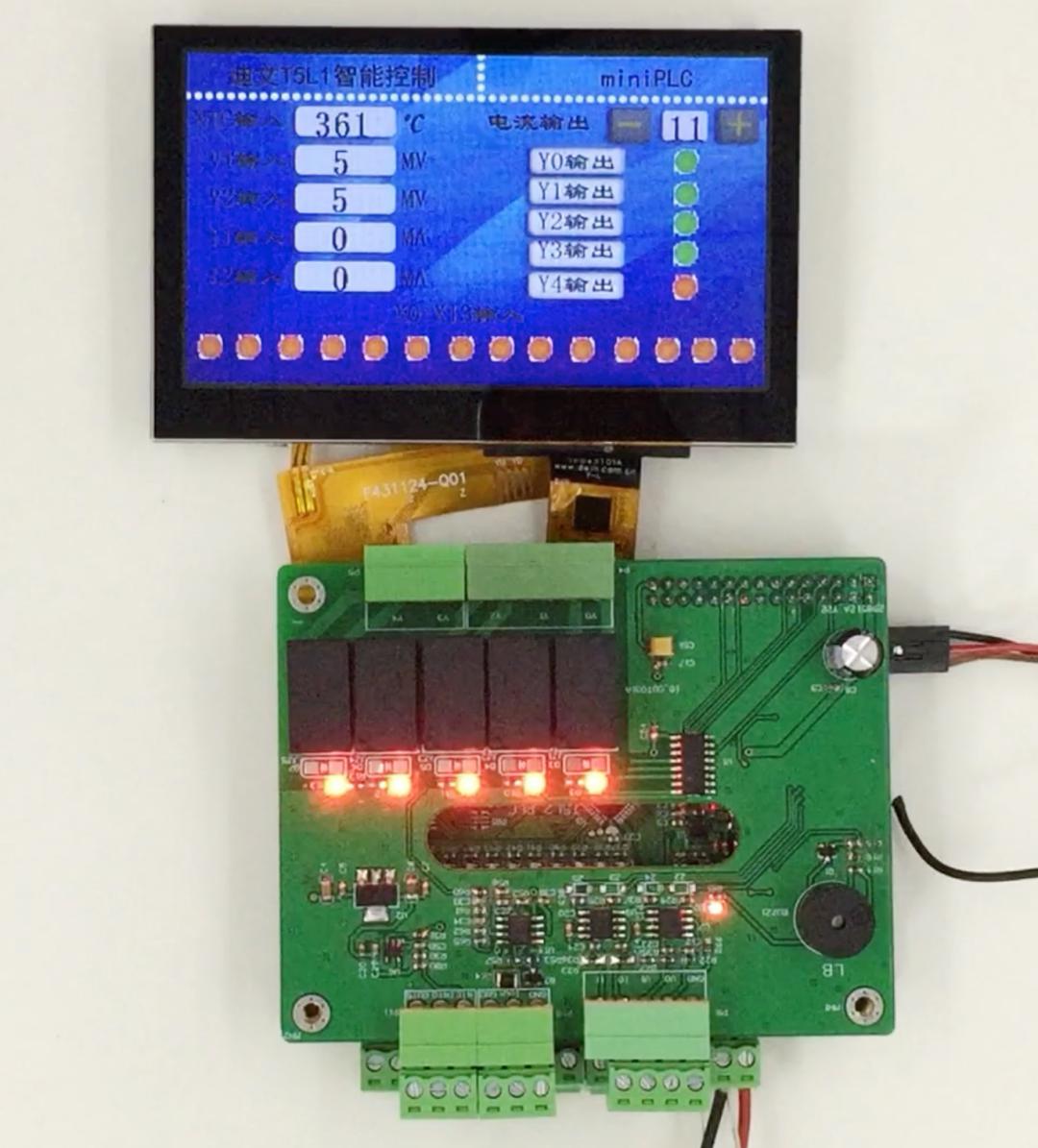

1.2 Veduta fiżika tal-effett

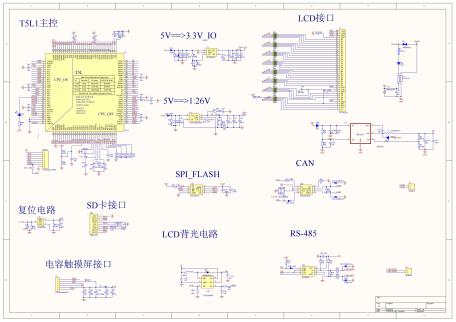

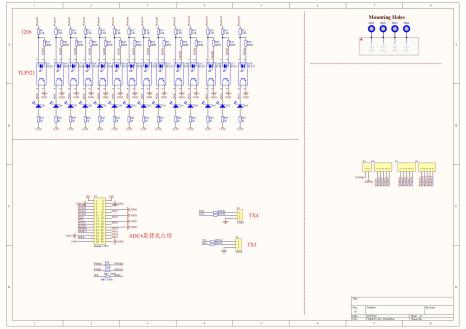

2. Disinn Skematiku

1.3 Skematika ta 'kontroll prinċipali

1.4 skematika IO

Il-kontroll tad-dawl ta 'wara tal-wiri jeħtieġ li jagħti attenzjoni lid-dawl ta' wara mixgħul, li jista 'jiġi kkontrollat bil-programm PWM tal-qalba tal-OS.It-tieni nett, l-inizjalizzazzjoni varjabbli ta 'xdata trid tiġi assenjata mill-ġdid wara l-inizjalizzazzjoni tas-sistema.

3.DGUSDisinn tal-Interface

1.5 Interfaċċja prinċipali

4.Video

Ħin tal-post: Lulju-05-2022